Zero

| 9) The control unit's Branch output will be 1 for a branch equal instruction. However, the branch's target address is only loaded into the PC if the ALU's Zero output is  Otherwise, PC is loaded with PC + 4.  0  1  (actually, Zero is not involved)                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

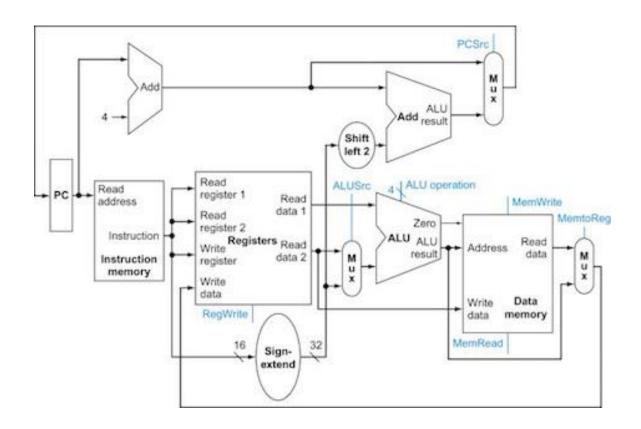

| Consider the above Figure 5.4.8 illustrating the datapath in action for a branch equal instruction                                                                                                                                                                                  |

| 10) The value for the ALUSrc control signal is  0 1                                                                                                                                                                                                                                 |

| 11) The value for the ALUOp control signal is  00 01                                                                                                                                                                                                                                |

| 12) Assume the current instruction is beq \$t1, \$t2, offset, and \$t1 is 90 while \$t2 is 85. The value for the Branch control signal is  0 1                                                                                                                                      |

| 13) Assume the current instruction is beq \$t1, \$t2, offset, and \$t1 is 90 while \$t2 is 85. The value for the Zero control signal is  0 1                                                                                                                                        |

| 14) Assume the current instruction is beq \$t1, \$t2, offset, and \$t1 is 90 while \$t2 is 85. How will the PC be updated next?  PC + 4  Target address                                                                                                                             |

| 115) The datapath shown requires four clock cycles to execute a branch instruction.  True False                                                                                                                                                                                     |

| 16) During a branch on equal instruction, two registers are read, those registers' values are subtracted. If the result is 0, Zero becomes 1, causing a new target address to pass through the mux on the upper right and be waiting to enter the PC on the next rising clock edge. |

<sup>C</sup> True

C False

17)

Highlight the active data path for:

• add \$4, \$5, \$6

Annotate the different segments of highlighted datapath with what they carry Assume the instruction is at memory location 0X1000, (\$4) = 0X9, and (\$5) = 0X6000, and (\$6) = 0X2040

After execution:

\$4 = \$5= \$6= PC=