#### EGC220 Digital Logic Fundamentals

# **Design Using Verilog**

#### **Baback Izadi**

Division of Engineering Programs bai@engr.newpaltz.edu

# **Basic Verilog**

- Lexical Convention

- Lexical convention are close to C++.

- Comment

- // to the end of the line.

- /\* to \*/ across several lines

- Keywords are lower case letter & it is **case sensitive**

- VERILOG uses 4 valued logic: 0, 1, x and z

- Comments: / / Verilog code for AND-OR-INVERT gate module <module\_name> (<module\_terminal\_list>); <module\_terminal\_definitions>

<functionality\_of\_module>

endmodule SUNY – New Paltz Elect. & Comp. Eng.

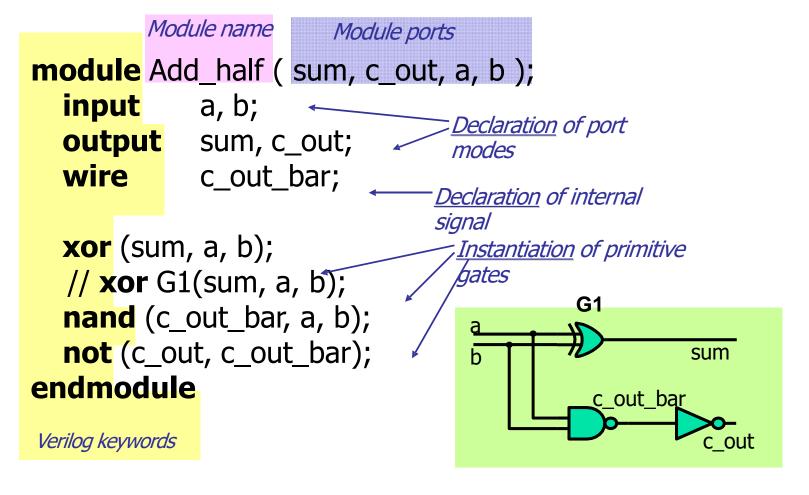

#### Taste of Verilog

SUNY – New Paltz Elect. & Comp. Eng. Lexical Convention

Numbers are specified in the traditional form or below .

<size><base format><number>

- Size: contains *decimal* digitals that specify the size of the constant in the number of bits.

- Base format: is the single character ' followed by one of the following characters b(binary),d(decimal),o(octal),h(hex).

• Number: legal digital.

#### Example :

- 347 -- decimal number

- 4'b101 -- 4- bit 0101<sub>2</sub>

- 2'012 -- 2-bit octal number

- 5'h87f7 -- 5-digit 87F7<sub>16</sub>

- 2'd83 -- 2-digit decimal

- String in double quotes " this is a introduction"

### Three Modeling Styles in Verilog

- Structural modeling (Gate-level)

- Use predefined or user-defined primitive gates.

- Dataflow modeling

- Use assignment statements (assign)

- Behavioral modeling

- Use procedural assignment statements (always)

#### Structural Verilog Description of Two-Bit Greater-Than Circuit

```

// Two-bit greater-than circuit: Verilog structural model

11

1

// See Figure 2-27 for logic diagram

11

2

module comparator_greater_than_structural(A, B, A_greater_than_B);

11

3

// 4

input [1:0] A, B;

5

output A greater than B;

11

wire B0_n, B1_n, and0_out, and1_out, and2_out;

6

11

11

7

not

inv0(B0_n, B[0]), inv1(B1_n, B[1]);

11

8

and

9

11

and0(and0_out, A[1], B1_n),

// 10

and1(and1_out, A[1], A[0], B0_n),

// 11

and2(and2_out, A[0], B1_n, B0_n);

// 12

// 13

or

or0(A_greater_than_B, and0_out, and1_out, and2_out);

// 14

endmodule

// 15

A1

B1

A0

-A greater than B

B0

Y – New Paltz

Copyright @2016 Pearson Education, All Rights Reserved

Elect. & Comp. Eng.

```

#### Dissection

#### Module and Port declarations

- Verilog-2001 syntax

- **module** AOI (input A, B, C, D, output F);

- Verilog-1995 syntax

- module AOI (A, B, C, D, F);

- input A, B, C, D;

- output F;

- Wires: Continuous assignment to an internal signal

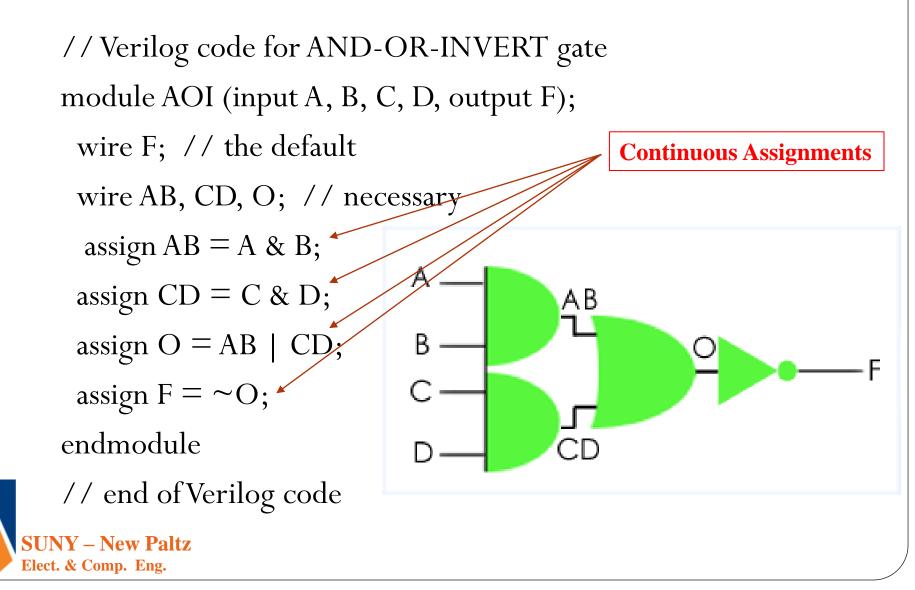

#### A Simple Dataflow Design

## A Simple Dataflow Design

// Verilog code for AND-OR-INVERT gate module AOI (input A, B, C, D, output F); assign  $F = \sim ((A \& B) | (C \& D));$

endmodule

// end of Verilog code

'&' for AND, '|' for OR, '^' for XOR '^~' for XNOR, '&~' for NAND

#### Dataflow Verilog Description of Two-Bit Greater-Than Comparator

```

// Two-bit greater-than circuit: Dataflow model

// 1

// See Figure 2-27 for logic diagram

11

2

module comparator_greater_than_dataflow(A, B, A_greater_than_B);

// 3

input [1:0] A, B;

// 4

11

5

output A_greater_than_B;

11

wire B1_n, B0_n, and0_out, and1_out, and2_out;

6

assign B1_n = ~B[1];

11 7

assign B0 n = \sim B[0];

// 8

assign and0 out = A[1] & B1 n;

11 9

assign and1 out = A[1] & A[0] & B0 n;

// 10

assign and2_out = A[0] & B1_n & B0_n;

// 11

assign A_greater_than_B = and0_out | and1_out | and2_out;

// 12

endmodule

// 13

```

# Conditional Dataflow Verilog Description of Two-Bit Greater-Than Circuit

```

// 1

// Two-bit greater-than circuit: Conditional model

1/ 2

// See Figure 2-27 for logic diagram

module comparator_greater_than_conditional2(A, B, A_greater_than_B);

1/ 3

input [1:0] A, B;

// 4

// 5

output A greater than B;

assign A_greater_than_B = (A > B)? 1'b1 :

11 6

1'b0:

// 7

endmodule

// 8

```

#### Verilog Description of Two-Bit Greater-Than Circuit

| // Two-bit greater-than circuit: Behavioral model                             | // 1 |

|-------------------------------------------------------------------------------|------|

| // See Figure 2-27 for logic diagram                                          | // 2 |

| <pre>module comparator_greater_than_behavioral(A, B, A_greater_than_B);</pre> | // 3 |

| <b>input [1:0]</b> A, B;                                                      | // 4 |

| <pre>output A_greater_than_B;</pre>                                           | // 5 |

| <pre>assign A_greater_than_B = A &gt; B;</pre>                                | // 6 |

| endmodule                                                                     | // 7 |

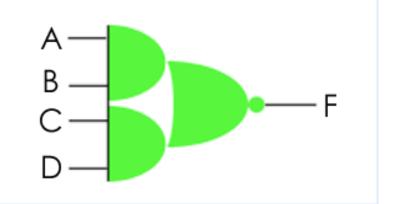

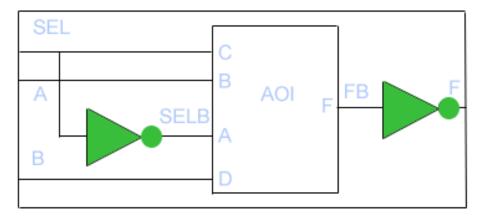

# A Design Hierarchy

- Module Instances

- MUX\_2 module contains references to each of the lower level modules

- // Verilog code for 2-input multiplexer

```

module MUX2 (input SEL, A, B, output F);

// 2:1 multiplexer

```

- // wires SELB and FB are implicit

- // Module instances...

- INV G1 (SEL, SELB);

```

AOI G2 (SELB, A, SEL, B, FB);

```

```

INV G3 (.A(FB), .F(F)); // Named mapping endmodule

```

// end of Verilog code

// Verilog code for 2-input multiplexer

module INV (input A, output F); // An inverter

assign F = ~A;

endmodule

module AOI (input A, B, C, D, output F); assign  $F = \sim ((A \& B) | (C \& D));$ endmodule

F = (SEL)'. A + (SEL).B

SELB = (SEL)'

F=(SELB).A + (SEL).B

1. Invert SEL and get SELB

2. Use AOI and get F'

3. Invert F' and get F

## **Another Example**

## **Hierarchical representation of Adder**

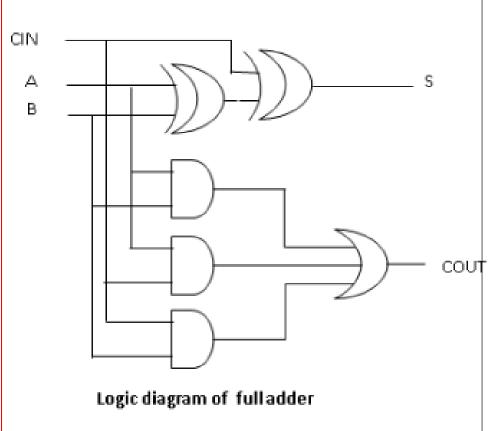

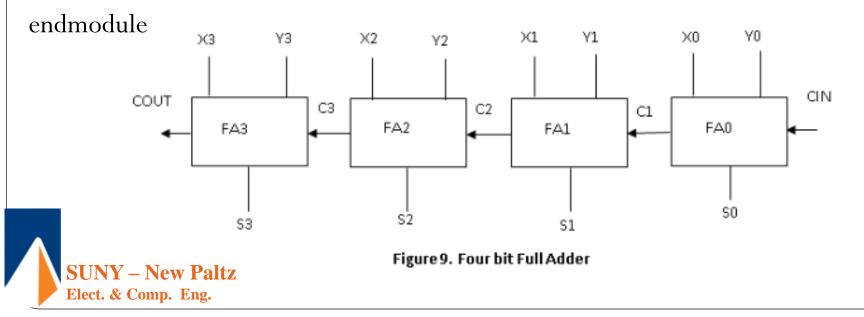

module fulladder (A, B, CIN, S, COUT); *input A*, *B*, *CIN*; output S,COUT; assign  $S = A \wedge B \wedge CIN$ ; assign COUT = (A & B) | (A & CIN)| *(B & CIN);* endmodule

```

module four_bit_adder (CIN, X3, X2, X1, X0, Y3, Y2, Y1, Y0, S3, S2, S1, S0, COUT);

```

- input CIN, X3, X2, X1, X0, Y3, Y2, Y1, Y0;

- output S3, S2, S1, S0, COUT;

```

wire C1, C2, C3;

```

fulladder FA0 (X0,Y0, CIN, S0, C1);

```

fulladder FA1 (X1,Y1, C1, S1, C2);

```

```

fulladder FA2 (X2,Y2, C2, S2, C3);

```

fulladder FA3 (X3,Y3, C3, S3, COUT);

```

module adder_4 (A, B, CIN, S, COUT);

input [3:0] A,B;

input CIN;

output [3:0] S;

output COUT;

wire [4:0] C;

full _adder FA0 (B(0), A(0), C(0), S(0), C(1));

full _adder FA1 (B(1), A(1), C(1), S(1), C(2));

full _adder FA2 (B(2), A(2), C(2), S(2), C(3));

full _adder FA3 (B(3), A(3), C(3), S(3), C(4));

assign C(0) = CIN;

Хl

Υ1

ΧŪ

YO

)(3

Y3

)(2

Y2

assign COUT = C(4);

CIN

endmodule

COUT

C3

C2

C1

FA3

FA2

FA1

FA0

S0

Y – New Paltz

S2

53

S1

Elect. & Comp. Eng.

Figure 9. Four bit Full Adder

```

#### **Verilog Statements**

Verilog has two basic types of statements

- Concurrent statements (combinational) (things are happening concurrently, ordering does not matter)

- Gate instantiations

- **and** (z, x, y), **or** (c, a, b), **xor** (S, x, y), etc.

- Continuous assignments

- **assign**  $Z = x \& y; c = a | b; S = x^y$

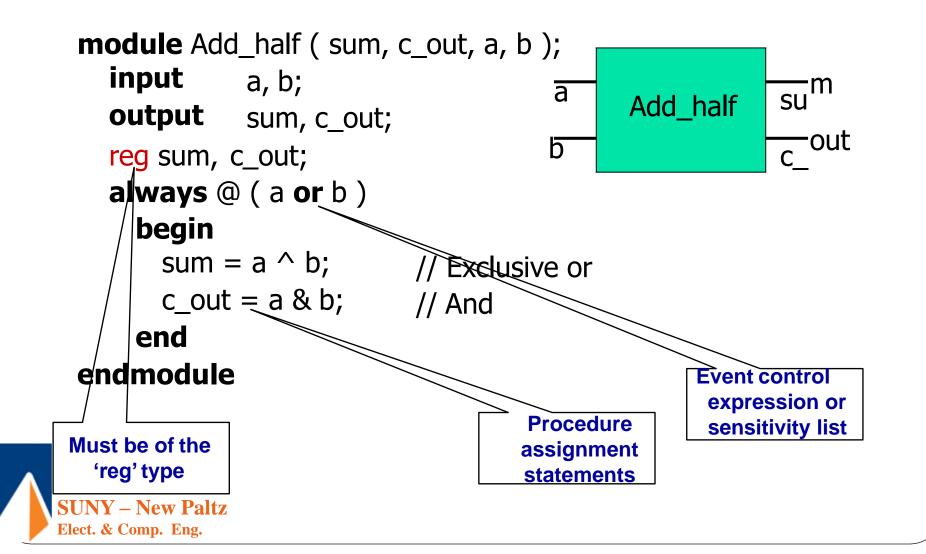

- 2. Procedural statements (sequential) (executed in the order written in the code)

- **always** (*a*) executed continuously when the event is active

- **Initial** executed only once (used in simulation)

- if then else statements

SUNY – New Paltz Elect. & Comp. Eng.

#### **Behavioral Description**

# **Conditional Statement**

• Conditional\_expression ? true\_expression : false expression;

#### **Example:**

- Assign  $A = (B \le C) ? (D+5) : (D+2);$

- if B is less than C, the value of A will be D + 5, or else A will have the value D + 2.

#### • An **if-else** statement is a procedural statement.

//Behavioral specification

module mux2to1 (w0, w1, s, F);

input wo,w1,s;

output F;

reg F;

always @ (w0,w1,s)if (s==1) F = w1; else F = w0; endmodule

always @ (w0,w1,s) F = s ? w1: w2;endmodule sensitivity list

#### Mux 4-to-1

```

module mux4to1 (w0, w1,w2, w3, S, F);

input w0,w1,w2,w3,[1:0] S;

output F;

reg F;

always (a) (w0,w1,w2,w3,S)

if (S==0) F = w0;

else if (S==1) F = w1;

else if (S==2) F = w^2;

else F = w3;

endmodule

New Paltz

```

Elect. & Comp. Eng.

| Verilog Operator                        | Name                                                                           | Functional Group  |  |

|-----------------------------------------|--------------------------------------------------------------------------------|-------------------|--|

| > >= < <=                               | greater than greater<br>than or equal to less<br>than less than or equal<br>to | relational        |  |

| == !=                                   | case equality case<br>inequality                                               | equality          |  |

| & ^                                     | bit-wise AND bit-wise<br>XOR bit-wise OR                                       | bit-wise bit-wise |  |

| &&                                      | logical AND logical<br>OR                                                      | logical           |  |

| SUNY – New Paltz<br>Elect. & Comp. Eng. |                                                                                |                   |  |

#### Another Example

```

//Dataflow description of a 4-bit comparator.

module mag_comp (A,B,ALTB,AGTB,AEQB);

input [3:0] A,B;

output ALTB, AGTB, AEQB;

assign ALTB = (A < B),

AGTB = (A > B),

AEQB = (A \equiv \equiv B);

endmodule

```

#### **Dataflow Modeling**

```

//Dataflow description of 4-bit adder

module binary_adder (A, B, Cin, SUM, Cout);

input [3:0] A,B;

input Cin;

output [3:0] SUM;

output Cout;

assign {Cout, SUM} = A + B + Cin;

endmodule

Binary addition

concatenation

Elect. & Comp. Eng.

```

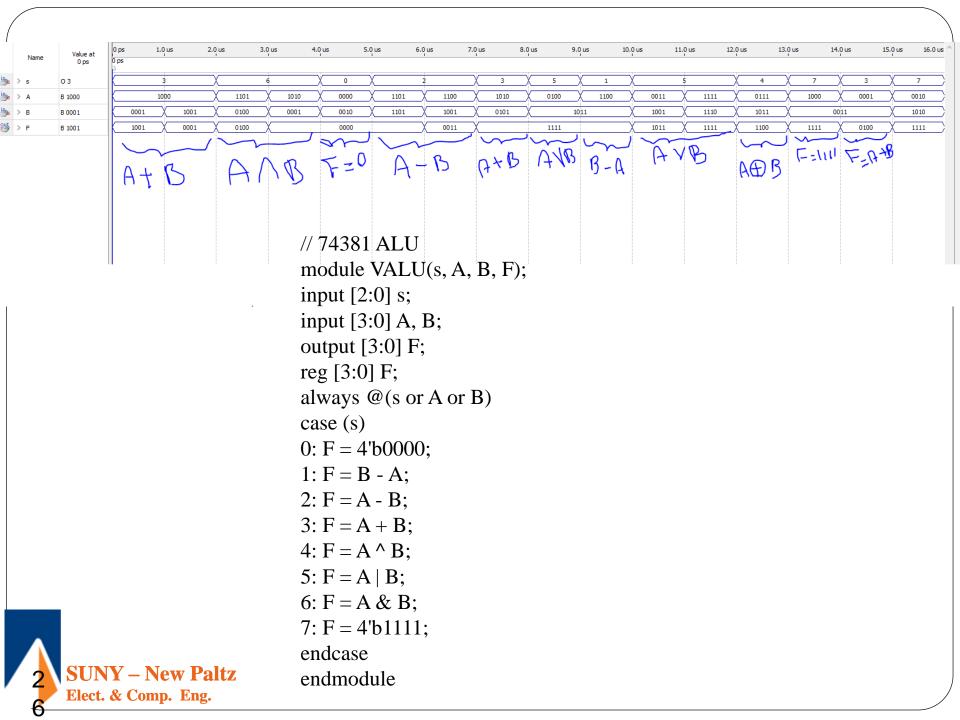

# Design of an ALU using Case Statement

| S | Function       |

|---|----------------|

| 0 | Clear          |

| 1 | B-A            |

| 2 | A-B            |

| 3 | A+B            |

| 4 | A XOR B        |

| 5 | A OR B         |

| 6 | A AND B        |

| 7 | Set to all 1's |

// 74381 ALU module alu(s, A, B, F); input [2:0] s; input [3:0] A, B; output [3:0] F; reg [3:0] F; always @(s or A or B) case (s) 0: F = 4'b0000;1: F = B - A;2: F = A - B;3: F = A + B;4:  $F = A^{A} B$ ; 5: F = A | B;6: F = A & B;7: F = 4'b1111; endcase endmodule

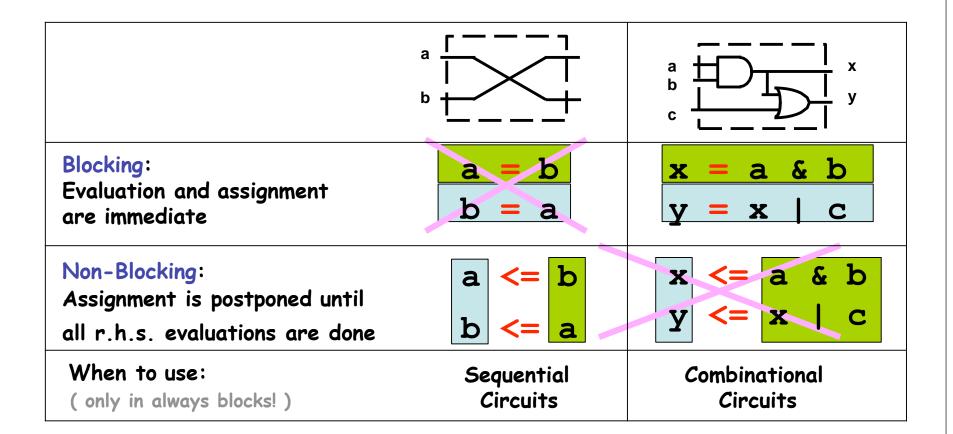

## Blocking vs. Nonblocking Assignments

- Verilog supports two types of assignments within *always* blocks, with subtly different behaviors.

- Blocking assignment: evaluation and assignment are immediate

always @ (a or b or c)

```

beginx = a | b;1. Evaluate a | b, assign result to xy = a ^ b ^ c;2. Evaluate a^b^c, assign result to yz = b & ~c;3. Evaluate b&(~c), assign result to zend

```

• *Nonblocking assignment:* all assignments deferred until all right-hand sides have been evaluated (end of simulation timestep)

```

always @ (a or b or c)

begin

x.<= a | b; 1. Evaluate a | b but defer assignment of x

y.<= a ^ b ^ c; 2. Evaluate a^b^c but defer assignment of y

b & ~c; 3. Evaluate b&(~c) but defer assignment of z

end

4. Assign x, y, and z with their new values

```

• Sometimes, as above, both produce the same result. Sometimes, not!

Y – New Paltz

Elect. & Comp. Eng.

## Blocking vs. Nonblocking Assignments

- The = token represents a blocking blocking procedural assignment

✓ Evaluated and assigned in a single step

- ✓ Execution flow within the procedure is blocked until the assignment is completed

- The <= token represents a non-blocking assignment</li>

✓ Evaluated and assigned in two steps:

- 1. The right hand side is evaluated immediately

- 2. The assignment to the left-hand side is postponed until other evaluations in the current time step are completed

```

//swap bytes in word

always @(posedge clk)

begin

word[15:8] = word[ 7:0];

word[ 7:0] = word[15:8];

end

```

```

//swap bytes in word

always @(posedge clk)

begin

word[15:8] <= word[ 7:0];

word[ 7:0] <= word[15:8];

end</pre>

```

#### Why two ways of assigning values?

Conceptual need for two kinds of assignment (in always blocks):

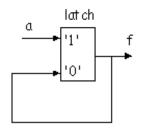

#### Golden Rules

#### • <u>Golden Rule 1:</u>

• To synthesize combinational logic using an always block, all inputs to the design must appear in the sensitivity list.

#### Golden Rule 2:

• To synthesize combinational logic using an always block, all variables must be assigned under all conditions.

#### Golden Rules

reg f; Reg f; always @ (sel, a, b) begin : begin f = b; if (sel == 1) f = a;f = a;else end f = b;end

Proper as intended

always @ (sel, a, b) if (sel == 1)

- Setting variables to default values at the start of the always block

- OK as well!

reg f; always @ (sel, a) begin : if (sel == 1)f = a;end

- What if sel = 0?

- Keep the current value •

- Undesired functionality •

- Unintended latch

- Need to include else

| Verilog    | Name                | Functional    | Verilog  | Name                  | Functional  |

|------------|---------------------|---------------|----------|-----------------------|-------------|

| Operator   |                     | Group         | Operator |                       | Group       |

| []         | bit-select or part- |               | +        | binary plus           | arithmetic  |

|            | select              |               | -        | binary minus          | arithmetic  |

| ()         | parenthesis         |               | <<       | shift left            | shift       |

| !          | logical negation    | logical       | >>       | shift right           | shift       |

| ~          | negation            | bit-wise      | >        | greater than          | relational  |

| &          | reduction AND       | reduction     | >=       | greater than or equal | relational  |

|            | reduction OR        | reduction     | <        | to                    | relational  |

| ~&         | reduction NAND      | reduction     | <=       | less than             | relational  |

| $\sim$     | reduction NOR       | reduction     |          | less than or equal to |             |

| Λ          | reduction XOR       | reduction     | ==       | case equality         | equality    |

| ~^ or ^~   | reduction XNOR      | reduction     | !=       | case inequality       | equality    |

| +          | unary (sign) plus   | arithmetic    | &        | bit-wise AND          | bit-wise    |

| -          | unary (sign) minus  | arithmetic    | ^        | bit-wise XOR          | bit-wise    |

| { }        | concatenation       | concatenation |          | bit-wise OR           | bit-wise    |

| $\{\{\}\}$ | replication         | replication   | &&       | logical AND           | logical     |

| *          | multiply            | arithmetic    |          | logical OR            | logical     |

| /          | divide              | arithmetic    | ?:       | conditional           | conditional |

| %          | modulus             | arithmetic    |          |                       |             |

#### Appendix

## **Arithmetic in Verilog**

module Arithmetic (A, B, Y1, Y2, Y3, Y4, Y5);

input [2:0] A, B; output [3:0]Y1;

**output** [4:0]Y3;

**output** [2:0]Y2,Y4,Y5;

**reg** [3:0]Y1;

**reg** [4:0]Y3;

**reg** [2:0]Y2,Y4,Y5;

always @(A or B)

begin

Y1=A+B;//addition

Y2=A-B;//subtraction

Y3=A\*B;//multiplication

Y4=A/B;//division

Y5=A%B;//modulus of A divided by B

#### end

endmodule SUNY – New Paltz Elect. & Comp. Eng.

# Sign Arithmetic in Verilog

**module** Sign (A, B, Y1, Y2, Y3);

input [2:0] A, B; output [3:0]Y1,Y2,Y3; reg [3:0]Y1,Y2,Y3;

always @(A or B)

begin

Y1=+A/-B; Y2=-A+-B; Y3=A\*-B;

end

### Equality and inequality Operations in Verilog

module Equality (A, B,Y1,Y2,Y3);

**input** [2:0] A, B;

output Y1,Y2;

**output** [2:0]Y3;

**reg** Y1,Y2;

**reg** [2:0]Y3;

always @(A or B)

begin

Y1=A==B;//Y1=1 if A equivalent to B Y2=A!=B;//Y2=1 if A not equivalent to B **if** (A==B)//parenthesis needed Y3=A;

else

Y3=B;

end

#### **Logical Operations in Verilog**

```

module Logical (A, B, C, D, E, F,Y);

input [2:0] A, B, C, D, E, F;

output Y;

reg Y;

always @(A or B or C or D or E or F)

begin

if ((A==B) && ((C>D) || !(E<F)))

Y=1;</pre>

```

else

Y=0;

end

#### **Bit-wise Operations in Verilog**

#### module Bitwise (A, B,Y);

**input** [6:0] A;

**input** [5:0] B;

**output** [6:0]Y;

**reg** [6:0]Y;

always @(A or B)

begin

Y[0]=A[0]&B[0]; //binary AND Y[1]=A[1]|B[1]; //binary OR Y[2]=!(A[2]&B[2]); //negated AND Y[3]=!(A[3]|B[3]); //negated OR Y[4]=A[4]^B[4]; //binary XOR Y[5]=A[5]~^B[5]; //binary XNOR Y[6]=!A[6]; //unary negation

#### end

# . Concatenation and Replication in Verilog

The concatenation operator "{ , }" combines (concatenates) the bits of two or more data objects. The objects may be scalar (single bit) or vectored (multiple bit). Multiple concatenations may be performed with a constant prefix and is known as replication.

```

module Concatenation (A, B,Y);

```

```

input [2:0] A, B;

output [14:0]Y;

parameter C=3'b011;

reg [14:0]Y;

always @(A or B)

begin

Y={A, B, {2{C}}, 3'b110};

```

end

# **Shift Operations in Verilog**

```

module Shift (A,Y1,Y2);

input [7:0] A;

output [7:0]Y1,Y2;

parameter B=3; reg [7:0]Y1,Y2;

always @(A)

begin

Y1=A<<B; //logical shift left

Y2=A>>B; //logical shift right

end

```

# **Conditional Operations in Verilog**

module Conditional (Time,Y);

```

input [2:0]Time;

output [2:0]Y;

reg [2:0]Y;

parameter Zero =3b'000;

parameter TimeOut = 3b'110;

always @(Time)

begin

Y=(Time!=TimeOut) ?Time +1 : Zero;

```

end

#### **Reduction Operations in Verilog**

**module** Reduction (A,Y1,Y2,Y3,Y4,Y5,Y6);

**input** [3:0] A; **output** Y1,Y2,Y3,Y4,Y5,Y6; **reg** Y1, Y2, Y3, Y4, Y5, Y6; always @(A) begin Y1=&A; //reduction AND Y2 = |A; //reduction ORY3=~&A; //reduction NAND  $Y4 = \sim |A; //reduction NOR$ Y5 = A; //reduction XORY6= $\sim^A$ ; //reduction XNOR

#### end

endmodule

SUNY – New Paltz Elect. & Comp. Eng.

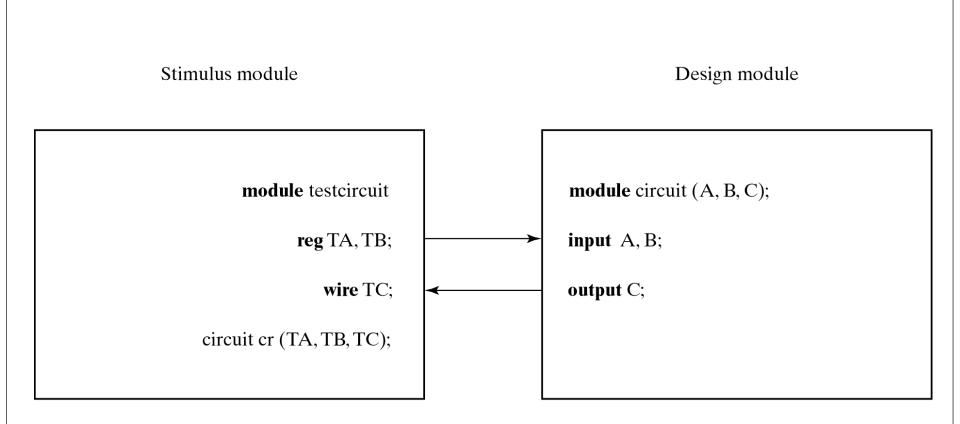

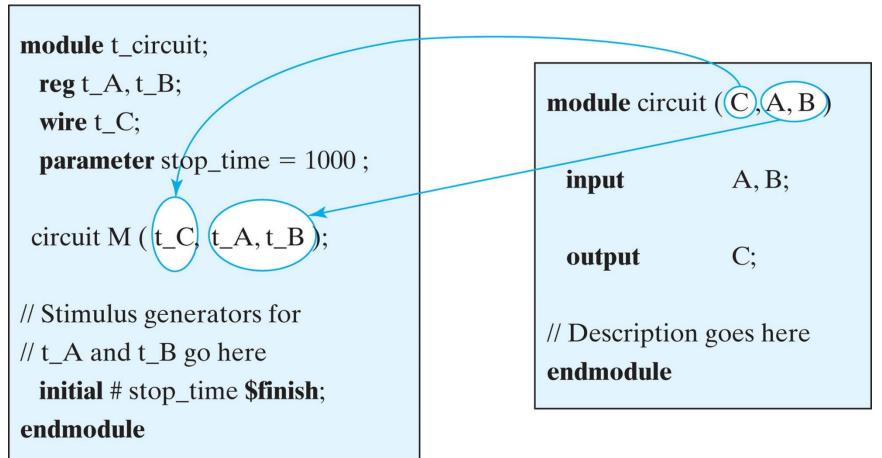

Fig. 4-33 Stimulus and Design Modules Interaction

# Testbench for the Structural Model of the Two-Bit Greater-Than Comparator

```

// Testbench for Verilog two-bit greater-than comparator

// 1

// 2

module comparator_testbench_verilog();

11 3

reg [1:0] A, B;

// 4

wire struct out;

// 5

comparator_greater_than_structural U1(A, B, struct_out);

initial

11 6

begin

// 7

A = 2'b10;

// 8

B = 2'b00;

11 9

// 10

#10;

B = 2'b01;

// 11

#10;

// 12

B = 2'b10;

// 13

#10;

// 14

B = 2'b11;

// 15

end

// 16

endmodule

// 17

```

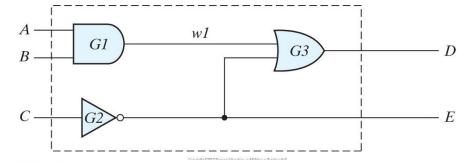

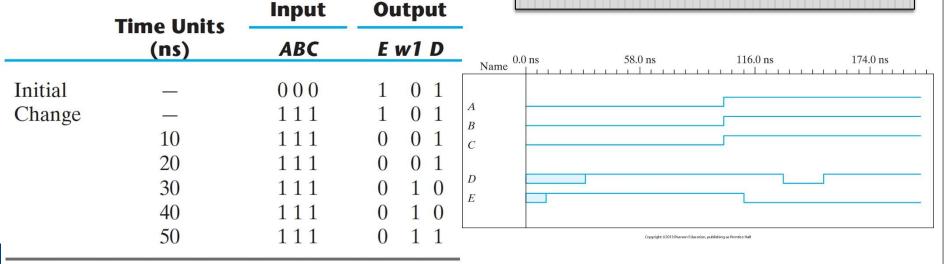

#### Circuit to demonstrate an HDL (Verilog)

Table 3.5Output of Gates after Delay

Module smpl\_Circuit (A, B, C, D, E) input A, B, C; output D, E; wire w1; and # (30) G1 (w1, A, B); not #10 G2 (E, C); or #(20) G3 (D, w1, E); endmodule

Copyright ©2012 Pearson Education, publishing as Prentice Hal

**SUNY – New Paltz**

Elect. & Comp. Eng.

# Interaction between stimulus and design modules

Copyright ©2013 Pearson Education, publishing as Prentice Hall