# **DUT Intro for Specman Elite Training**

## **Objectives**

- By the end of this intro you will be familiar with the router DUT:

- Input Protocol

- Output Protocol

DUT Specification 2/11

## Contents

- A bird's view of the DUT

- DUT Specification

- Input Protocol

- Output Protocol

- Signal Name Appendix

- DUT State Machine

DUT Specification 3/11

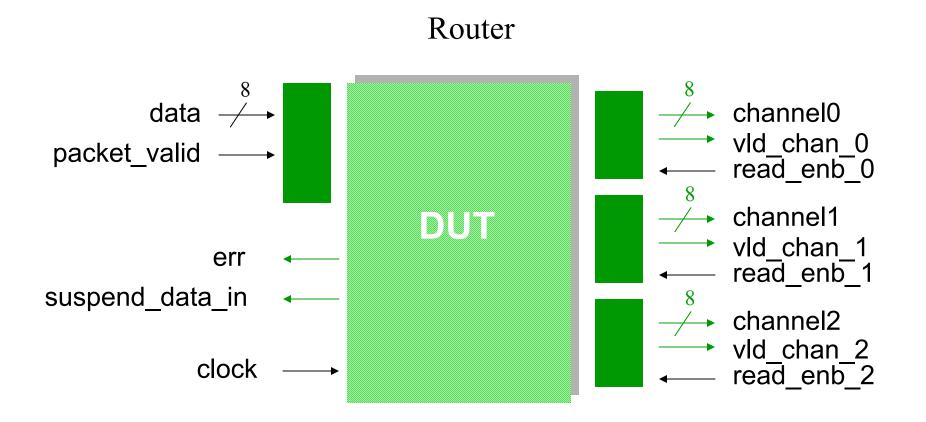

## A bird's view of the DUT

DUT Specification 4/11

## **DUT Specification**

The router accepts data packets on a single input port, data, and routes the packets to one of three output channels: channel0, channel1, or channel2.

A packet is a sequence of bytes with the first byte containing a header, the next variable set of bytes containing data, and the last byte containing parity. The header consists of a 2-bit address field and a 6-bit length field. The address field is used to determine to which output channel the packet should be routed to, with address "3" being illegal. The length field specifies the number of data bytes (payload). A packet can have a minimum data size of 1 byte and a maximum data size of 63 bytes. The parity should be a byte of even, bitwise parity, calculated over the header and data bytes of the packet. The format of a packet is shown in the figure.

# Packet Structure 7 6 5 4 3 2 1 0 length addr addr Byte 0 Header data[0] Byte 1 Payload

data[N]

Byte N+1 ←

parity

Byte N+2 ← Parity

## Input Protocol

H = Header, D = Data, P = Parity

All **input** signals are active high and are synchronized to the **falling** edge of the clock. The packet\_valid signal has to be asserted on the same clock when the first byte of a packet (the header byte), is driven onto the data bus. Since the header byte contains the address, this tells the router to which output channel the packet should be routed. Each subsequent byte of data should be driven on the data bus with each new falling clock. After the last payload byte has been driven, on the next falling clock, the packet\_valid signal must be deasserted (before the parity byte is driven). The packet parity byte should be driven on the next falling clock edge. The input data cannot change while suspend\_data\_in signal is active (indicating a FIFO overflow). The err signal asserts when a packet with bad parity is detected.

SBT Specification 6/11

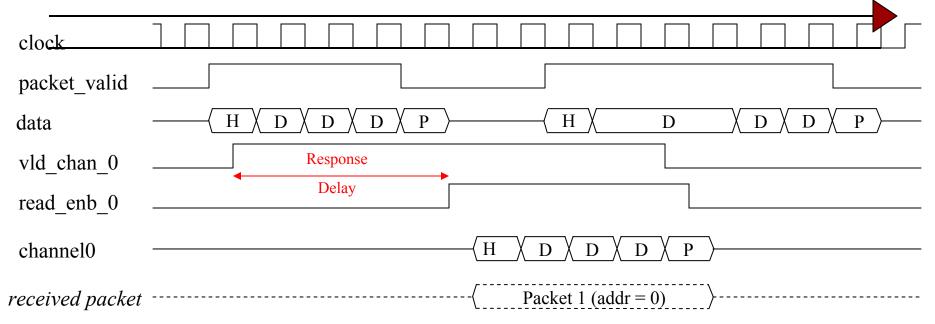

# Output Protocol - (Example: port 0)

H = Header, D = Data, P = Parity

All **output** signals are active high and are synchronized to the **falling** edge of the clock. Each output port is internally buffered by a FIFO of depth 16 and a width of 1 byte. The router asserts the vld\_chan\_x signal when valid data appears on the channelx output bus. The read\_enb\_x input signal must then be asserted on the falling clock edge in which data is read from the channelx bus. Read\_enb\_x must be asserted within 30 cycles. As long the read\_enb\_x signal remains active, the channelx bus drives a valid packet byte on each rising clock edge.

DUT Specification 7/11

# Signal Name Appendix

#### Signal Name

top/data top/packet\_valid top/clock top/read\_enb\_0 top/read\_enb\_1 top/read\_enb\_2 top/err top/suspend\_data\_in top/channel0 top/vld\_chan\_0 top/vld\_chan\_1 top/channel2 top/vld\_chan\_2

#### **Function**

Input bus - 8 bits Input - 1 bit Output - 1 bit Output - 1 bit Output - 1 bit Output - 8 bits Output - 1 bit Output - 1 bit Output - 1 bit Output - 1 bit Output - 8 bits Output - 1 bit Output - 8 bits Output - 1 bit

#### <u>Signal Name</u>

top/router1/in\_port/state top/router1/queue\_0/full top/router1/queue\_1/full top/router1/queue\_2/full top/router1/queue\_0/read\_ptr top/router1/queue\_1/read\_ptr top/router1/queue\_2/read\_ptr top/router1/queue\_0/write\_ptr top/router1/queue\_1/write\_ptr top/router1/queue\_2/write\_ptr

#### **Function**

State Machine – enum type Ch 0 FIFO Full flag – bit Ch 1 FIFO Full flag – bit, Ch 2 FIFO Full flag – bit Ch 0 read addr pointer – 4 bits Ch 1 read addr pointer – 4 bits Ch 2 read addr pointer – 4 bits Ch 0 read addr pointer – 4 bits Ch 1 read addr pointer – 4 bits Ch 1 read addr pointer – 4 bits Ch 1 read addr pointer – 4 bits

DUT Specification 8/11

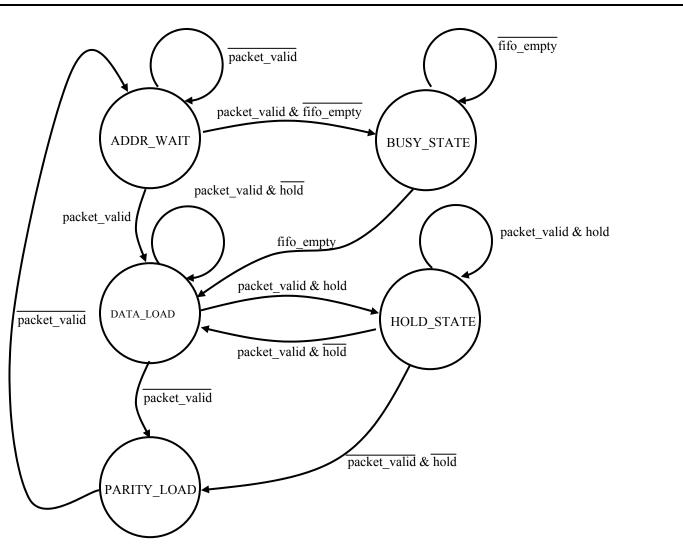

## State Machine

SBT Specification 9/11

## State Machine (cont.)

### **LEGAL STATE TRANSITIONS**

| Current State      | Next State                         |

|--------------------|------------------------------------|

| $ADDR_WAIT = 0x0$  | ADDR_WAIT, DATA_LOAD, BUSY_STATE   |

| $DATA\_LOAD = 0x1$ | DATA_LOAD, PARITY_LOAD, HOLD_STATE |

| PARITY_LOAD = 0x2  | ADDR_WAIT                          |

| HOLD_STATE = 0x3   | HOLD_STATE, DATA_LOAD, PARITY_LOAD |

| BUSY_STATE = 0x4   | BUSY_STATE, DATA_LOAD              |

DUT Specification 10/11

## Summary

Now you know the course sample DUT:

- ✓ DUT Specification

- ✓ Input Protocol

- ✓ Output Protocol

- ✓ Signal Name Appendix

- ✓ DUT State Machine

DUT Specification 11/11